I am a Ph.D. student in the School of Electronic and Electrical Engineering at Kyungpook National University  , advised by Prof. Daejin Park

, advised by Prof. Daejin Park  from Sep. 2019. I received a bachelor’s degree of Electronics Engineering from the same university at Aug. 2019 (ealry graduation).

from Sep. 2019. I received a bachelor’s degree of Electronics Engineering from the same university at Aug. 2019 (ealry graduation).

My research mainly focuses on efficient accelerators for MCU, AP architecture, with contributions in:

SWFWEfficient MCU firmware: I have worked extensively on tackling challenges for on-chip flash firmware update, such as robustness, and efficiency. My work includes achieving efficient IoT sensor nodes.HWEfficient hardware design: I work to comprehensively mitigate hardware overhead, including Armv6 ISA compatible CNN accelerators, ADC error compensation with MLP, and customized accelerator controllers. Some of my recent work, including MPW chips, is currently under review.HWSWEfficient software-embedded SoC verification platform: My work includes an emulator-simulator mixed framework to speed up partial RTL verification within SoCs driven by embedded software.HWAutomotive IP RTL Design: My work includes communication interface module RTL design and AMBA bus integration for automotive sensor ASICs, such as DSI3, SENT, I2S.

My research aims to achieve efficient AI accelerator utilization and virtualization by tightly-coupling all full-stack layers of HW, SW, and OS. My 20+ published papers

I was selected as the first integrated B.S./M.S./Ph.D. student at university and was awarded a Ph.D. Research Fellowship from the National Research Foundation (NRF) of Korea.

I am currently seeking postdoctoral opportunities. If you have any advice or are interested in exploring academic collaborations, please feel free to read my CV and contact me. I look forward to your insights and suggestions.

📝 Publications

1️⃣ Efficient Firmware

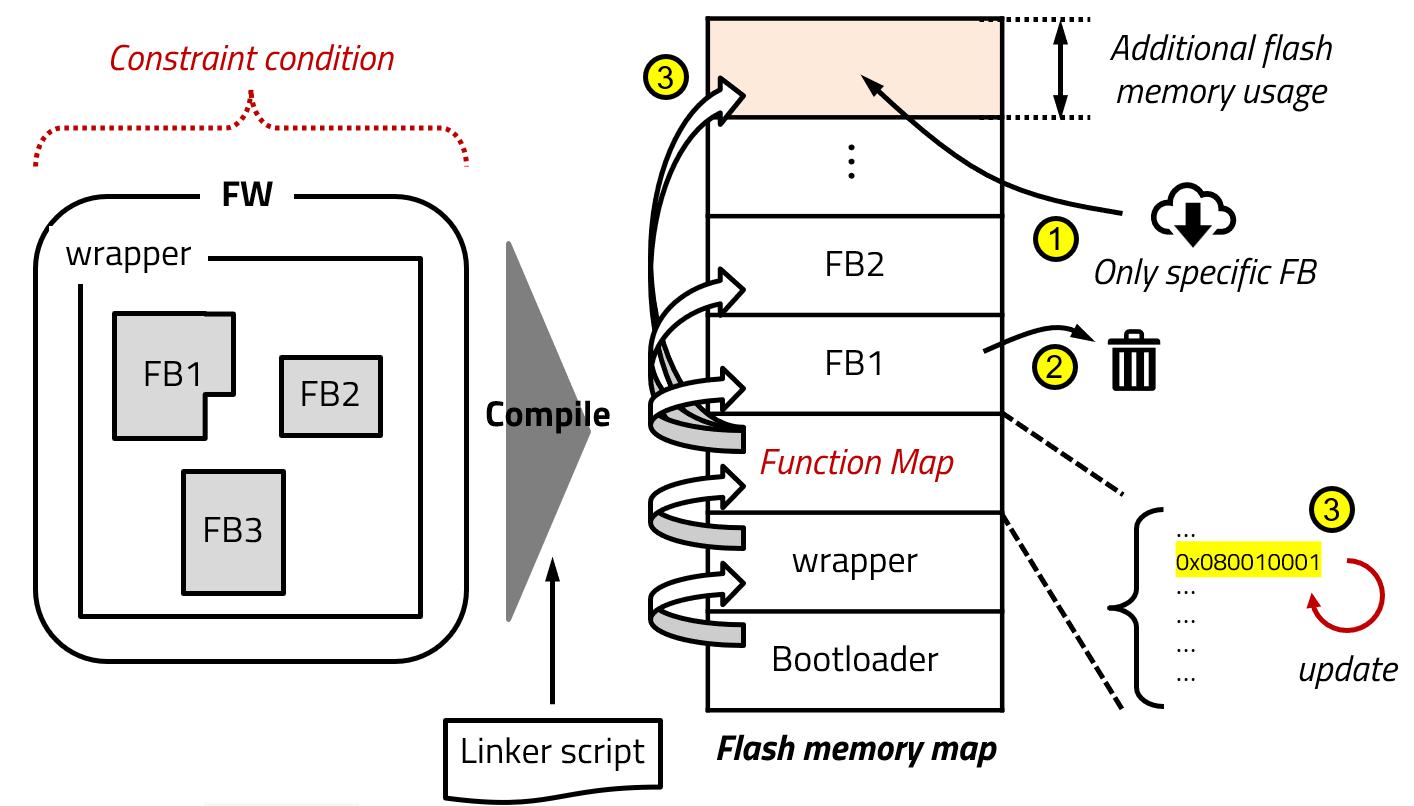

[IEICE TE’21] Low-Power Fast Partial Firmware Update Technique of On-Chip

Flash Memory for Reliable Embedded IoT Microcontroller

Jisu Kwon, Moon Gi Seok, and Daejin Park

-

Low-power, fast partial firmware update using function maps for efficient on-chip flash memory management.

-

Function map enables efficient updates by modifying block addresses without rewriting whole memory.

-

Reduces update time, energy use, and memory overhead in IoT microcontrollers.

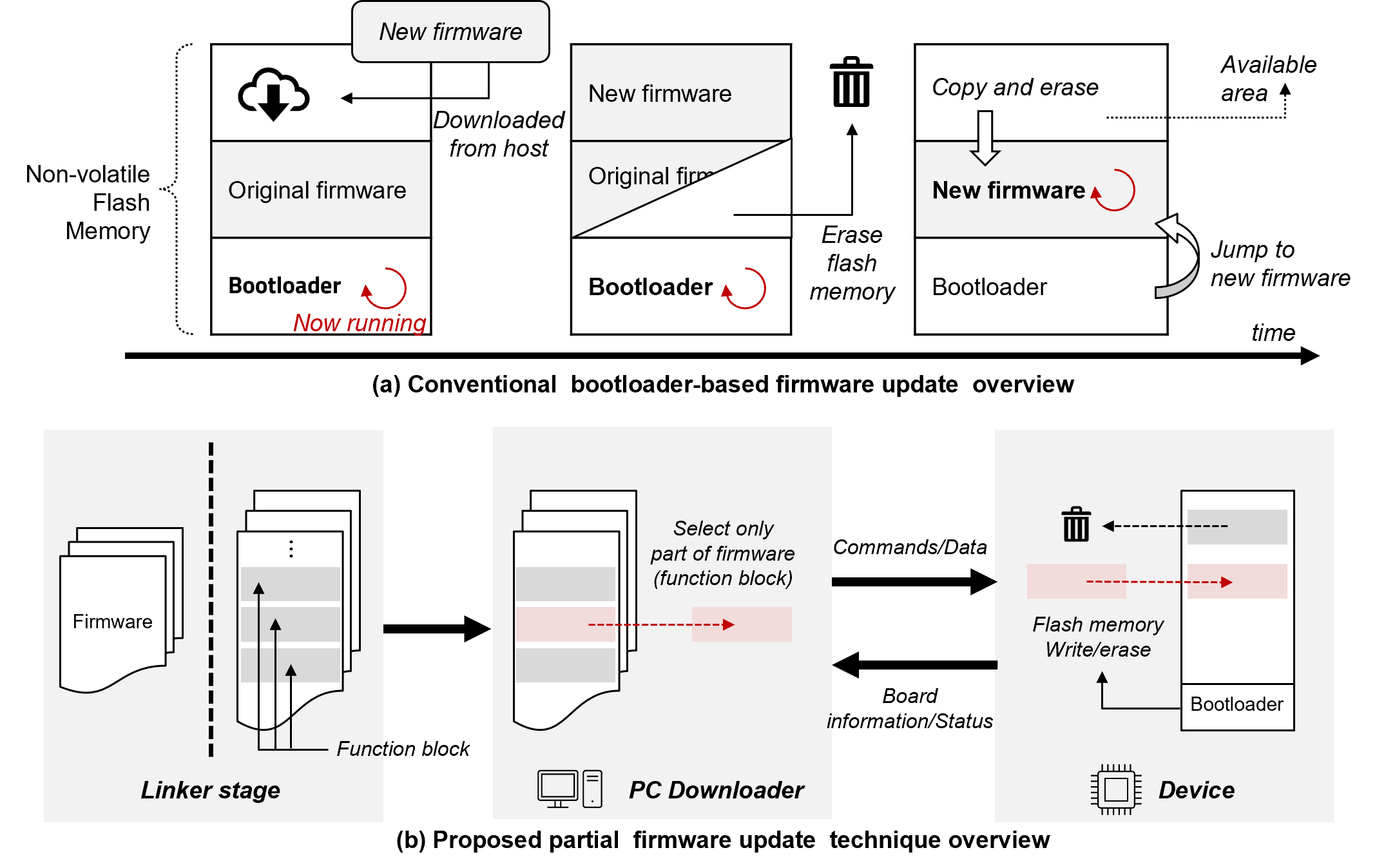

[IEEE COOLChips’20] User Insensible Sliding Firmware Update Technique for

Flash-Area/Time-Cost Reduction toward Low-Power Embedded Software Replacement

Jisu Kwon, Moon Gi Seok, and Daejin Park

-

User insensible sliding firmware update reduces flash memory usage and device pause time by updating only function blocks instead of entire firmware.

-

Achieves 63.64% memory overhead reduction, 79.98% pause time reduction, and 78.78% energy consumption reduction.

-

Sensors’23Optimized Replication of ADC-Based Particle Counting Algorithm with Reconfigurable Multi-Variables in Pseudo-Supervised Digital Twining of Reference Dust Sensor Systems, Seungmin Lee, Jisu Kwon, and Daejin Park. -

IEEE Access’23Runtime Tracking-Based Replication of On-Chip Embedded Software Using Transfer Function Learning for Dust Particle Sensing Systems, Seungmin Lee, Jisu Kwon, and Daejin Park. IEEE Access’22Efficient Sensor Processing Technique Using Kalman Filter-Based Velocity Prediction in Large-Scale Vehicle IoT Application, Jisu Kwon, and Daejin Park.IEEE ICAIIC’22Implementation of Computation-Efficient Sensor Network for Kalman Filter-based Intelligent Position-Aware Application, Jisu Kwon, and Daejin Park.IEEE ICCE-Asia’20Segmented Polynomial Approximation for Controlled System Characteristic Estimation on Lightweight Edge Device, Minsung Kim, Jongheon Baek, Jiwoong Jung, Jisu Kwon, and Daejin Park.IEEE ISPACS’19Function Block-Based Robust Firmware Update Technique for Additional Flash-Area/Energy-Consumption Overhead Reduction, Jisu Kwon, Jeonghun Cho, and Daejin Park.IEEE COOLChips’19Efficient Flash Memory Access Power Reduction Techniques for IoT-Driven Rare-Event Logging Application, Jisu Kwon, Jeonghun Cho, and Daejin Park. (Poster Session)

2️⃣ Efficient Hardware

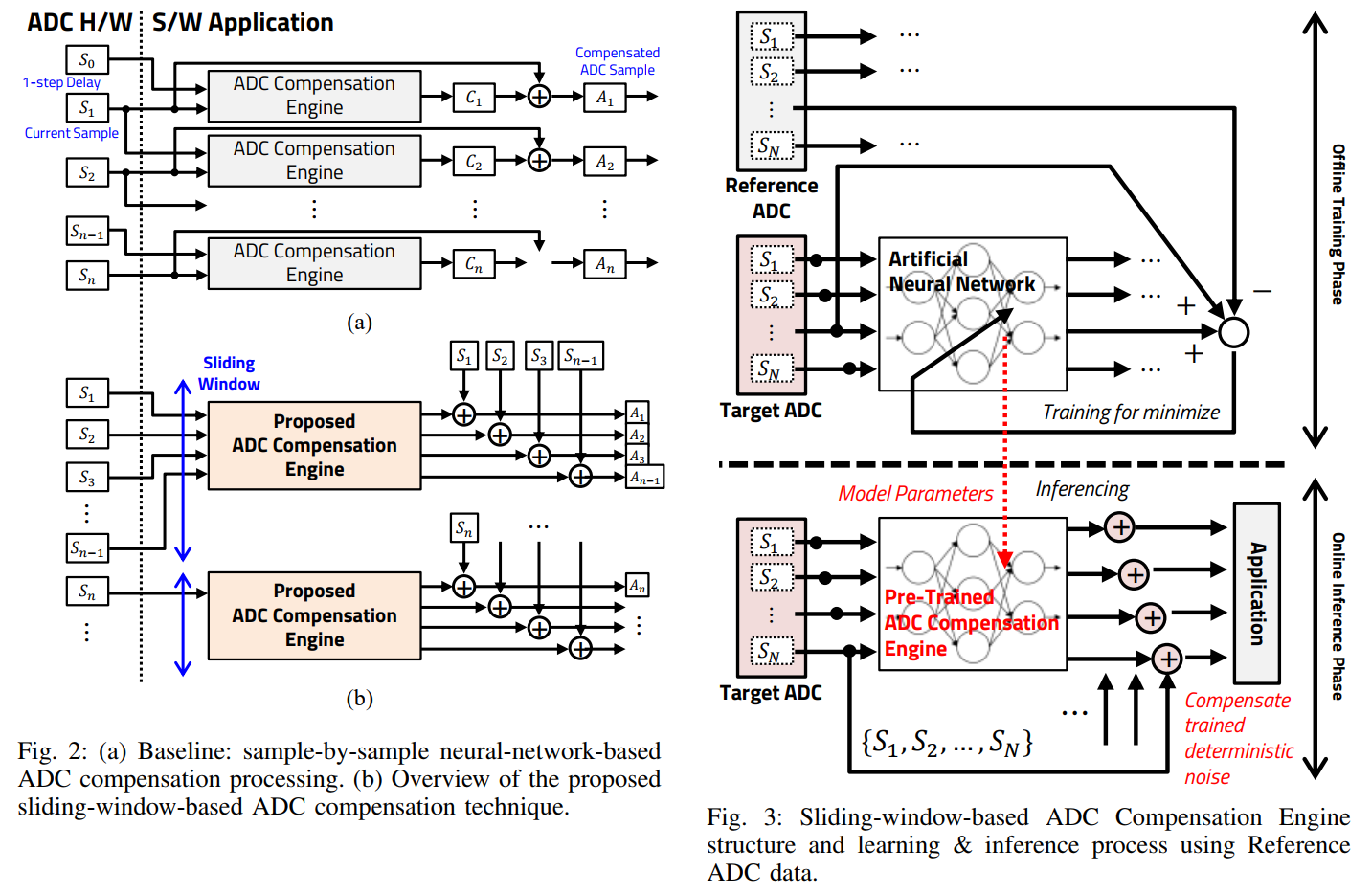

[VLSI-TSA’25] Sliding-Window-based Fast and Lightweight ADC Pseudo-Randomness

Compensation Technique for Low-Cost ADC

Jisu Kwon, and Daejin Park

Slides

|

Poster

-

Sliding-window-based ADC compensation reduces noise using neural networks.

-

Minimizes hardware usage, enhances ADC performance with software compensation.

-

Achieves 1.61× ENOB improvement, 5.82× processing time reduction under 20 dB noise.

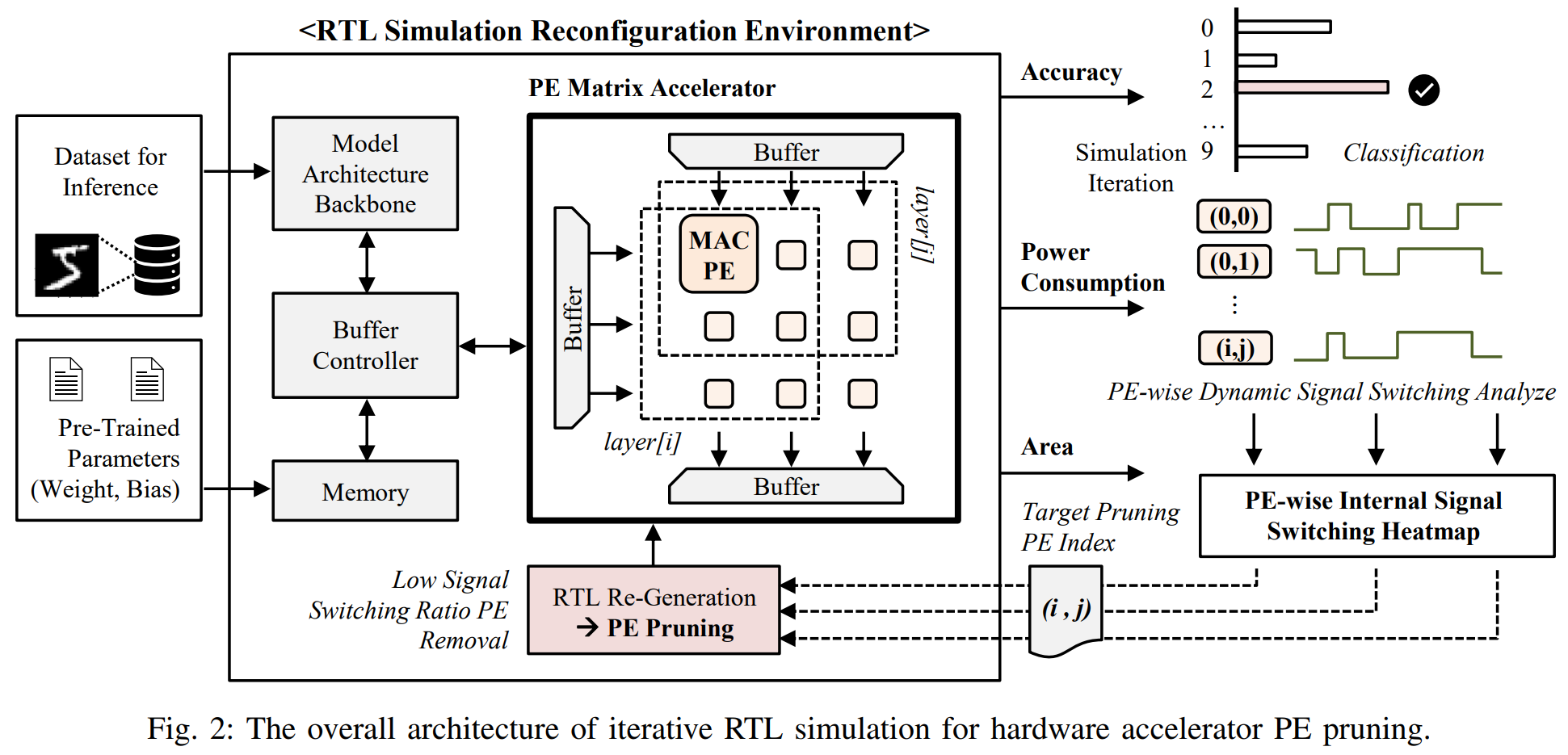

[IEEE MWSCAS’23] Hardware Accelerator Processing Element Unit Dynamic Pruning using

Runtime RTL Simulation Reconfiguration

Jisu Kwon, Heuijee Yun, and Daejin Park

-

Dynamic MAC unit pruning reduces neural accelerator area and power consumption by removing inactive processing elements.

-

Empirical RTL simulation analyzes signal switching to optimize pruning while maintaining accuracy.

-

Achieves up to 9.78% signal switching reduction, 4.25% area savings, and only 1% accuracy loss.

-

Applied Sciences’22Hardware/Software Co-Design for TinyML Voice-Recognition Application on Resource Frugal Edge Devices, Jisu Kwon, and Daejin Park. -

ISOCC’22Lightweighted AI-based Inference using Deterministic Randomness Compensation for Microcontroller ADC Resolution Enhancement, Jisu Kwon, and Daejin Park. -

JIPS’20GPU-Based ECC Decode Unit for Efficient Massive Data Reception Acceleration, Jisu Kwon, Moon Gi Seok, and Daejin Park.

3️⃣ SoC Verification

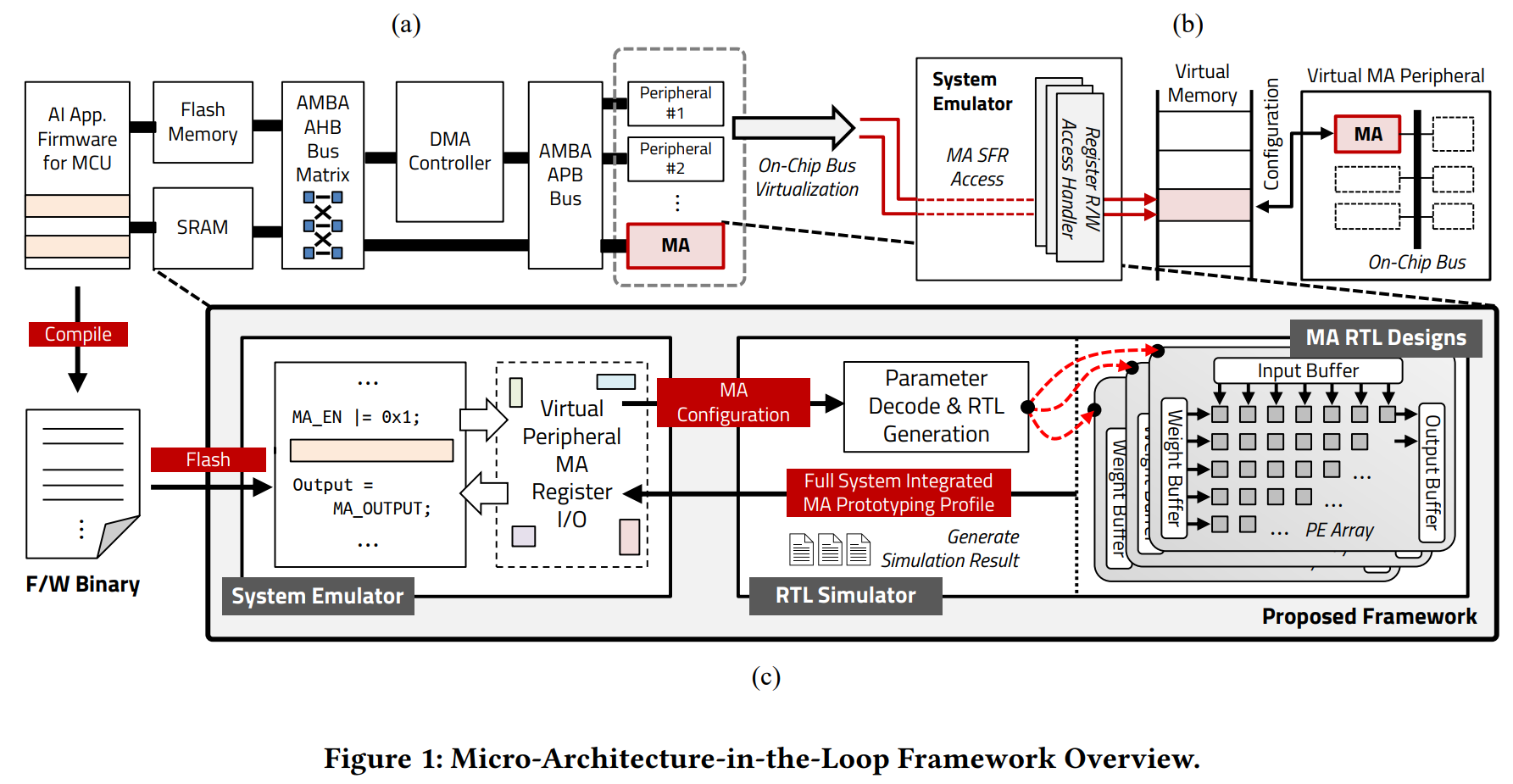

[Applied Sciences’25] MAIL: Micro-Accelerator-in-the-Loop Framework for MCU Integrated

Accelerator Peripheral Fast Prototyping

Jisu Kwon, and Daejin Park

- Micro-Accelerator-in-the-Loop (MAIL) framework enables fast prototyping of MCU-integrated accelerators for TinyML.

- Combines software emulation and cycle-accurate RTL simulation to evaluate hardware-software interaction.

- Supports parameter exploration for optimizing accelerator performance and resource usage.

- Reduces latency and improves efficiency in TinyML applications.

[ACM/IEEE EMSOFT’23] Work-in-Progress: Micro-Accelerator-in-the-Loop Framework for MCU

Integrated Accelerator Peripheral Fast Prototyping

Jisu Kwon, and Daejin Park

(BK21+ CS SCI Conference) | Slides | Poster

-

Micro-Accelerator-in-the-Loop (MAIL) framework enables fast prototyping of MCU-integrated accelerators.

-

Combines system emulation and cycle-accurate RTL simulation for efficient performance profiling.

-

Achieves up to 84.32% and 61.32% cycle latency reduction in TinyML applications.

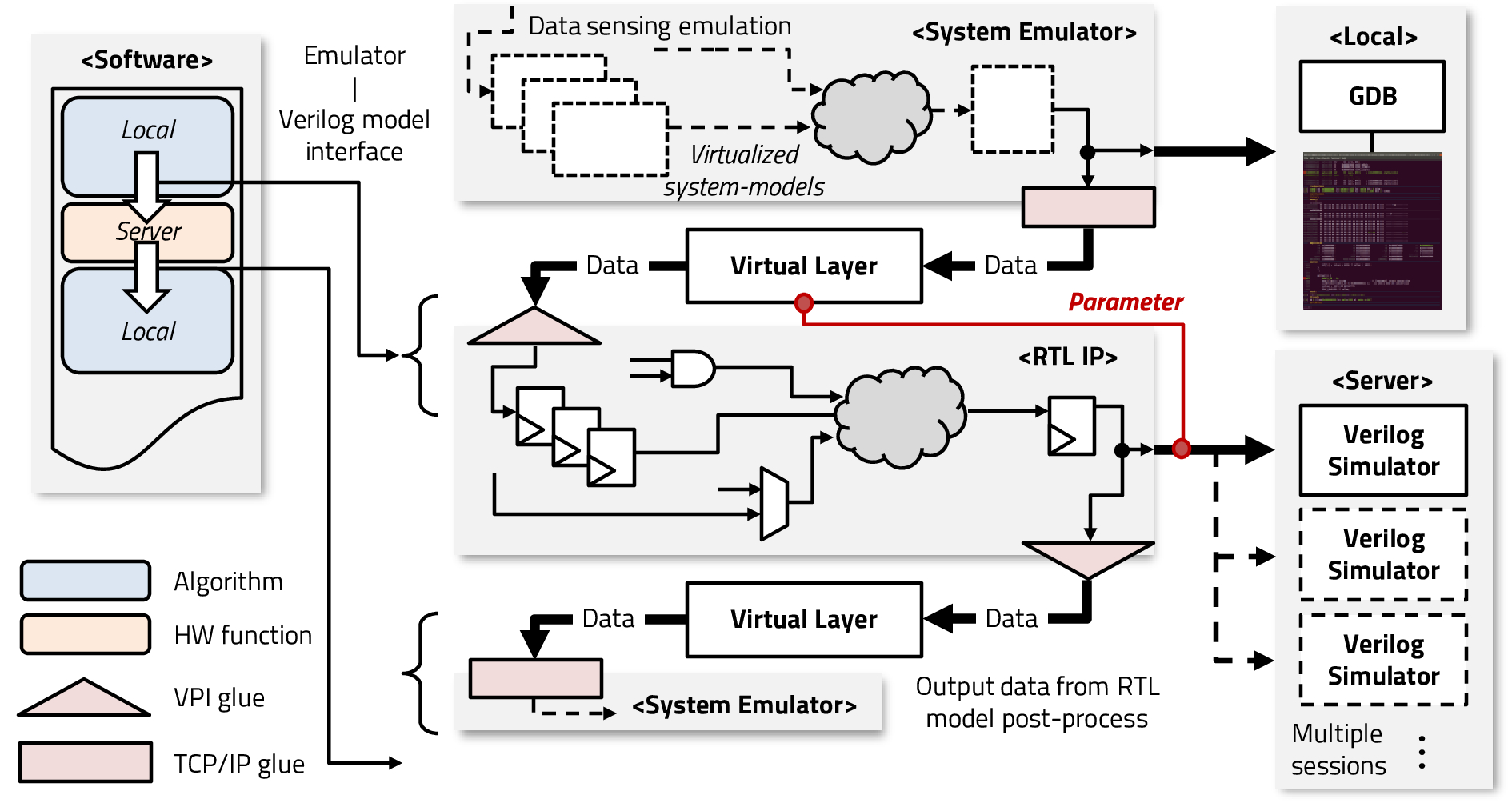

[IEEE ISCAS’21] Metamorphic Edge Processor Simulation Framework Using Flexible

Runtime Partial Replacement of Software-Embedded Verilog RTL Models,

Jisu Kwon, Sejong Oh, and Daejin Park

-

Metamorphic edge processor simulation framework accelerates RTL verification by replacing redundant models with software emulation.

-

Virtual layer enables dynamic partial RTL model replacement at runtime.

-

Achieves significant simulation speedup while maintaining parameter exploration flexibility.

IEEE ICAIIC’25A Dynamic Linking Framework for Efficient QEMU Peripheral Development and Maintenance, Gihyeon Jeon, Jisu Kwon, and Daejin Park.

4️⃣ TinyML

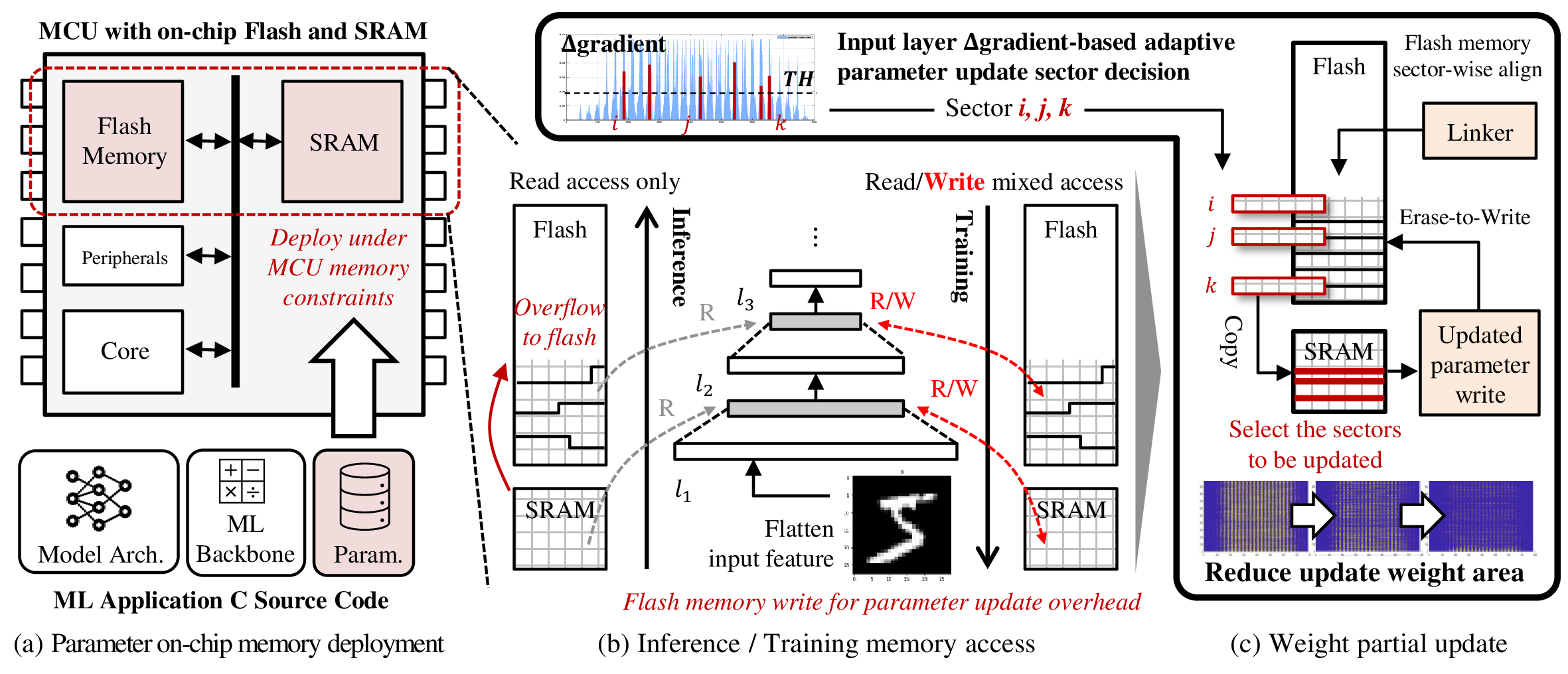

[IEEE ESL’23] Efficient Partial Weight Update Techniques for Lightweight On-Device Learning

on Tiny Flash-Embedded MCUs

Jisu Kwon, and Daejin Park

-

Partial weight update technique reduces memory usage in on-device learning by updating only selected weights stored in flash.

-

Gradient-based selection minimizes accuracy loss while optimizing SRAM usage.

-

Achieves 76.1% accuracy with only 18.52% weight updates, reducing APDP by up to 46.9%.

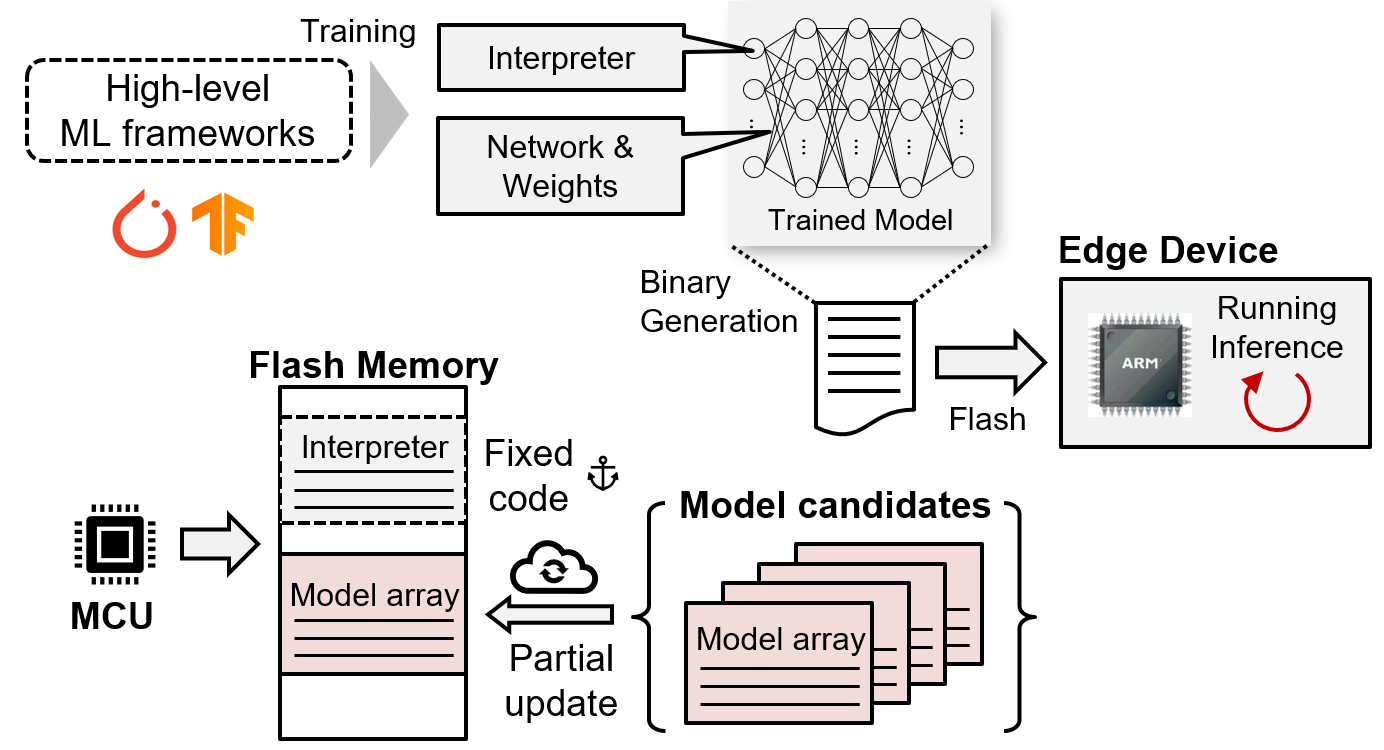

[HPC-Asia’21] Toward Data-Adaptable TinyML Using Model Partial Replacement for Resource

Frugal Edge Device

Jisu Kwon, and Daejin Park

-

Model partial replacement enables data-adaptable TinyML by updating only specific network components in resource-limited edge devices.

-

Reduces model size, maintains accuracy, and optimizes flash memory usage.

-

Enhances inference efficiency without full firmware updates.

IEEE ISPACS’22Neural Network-based Approximate Quality Prediction for Parameter Exploration in Industrial Manufacturing, Jisu Kwon, Moon Gi Seok, and Daejin Park.

️5️⃣️ Others

ACM TMCS’25Hyperparameter Tuning with Gaussian Processes for Optimal Abstraction Control in Simulation-based Optimization of Smart Semiconductor Manufacturing Systems, Moon Gi Seok, Wen Jun Tan, Wentong Cai, Jisu Kwon, and Seon Han Choi.

6️⃣ Domestic Journal Articles

IEMEK JESA’22Collaborative Streamlined On-Chip Software Architecture on Heterogenous Multi-Cores for Low-Power Reactive Control in Automotive Embedded Processors, Jisu Kwon, and Daejin Park.-

JKIICE’21Low-Power Metamorphic MCU using Partial Firmware Update Method for Irregular Target Systems Control, Jongheon Baek, Jiwoong Jung, Minsung Kim, Jisu Kwon, and Daejin Park. -

JKIICE’20Acceleration of ECC Computation for Robust Massive Data Reception under GPU-based Embedded Systems, Jisu Kwon, and Daejin Park. -

JKIICE’20Velocity and Distance Estimation-based Sensing Data Collection Interval Control Technique for Vehicle Data-Processing Overhead Reduction, Jisu Kwon, and Daejin Park. IEMEK JESA’19Efficient Flash Memory Access Power Reduction Techniques for IoT-Driven Rare-Event Logging Application, Jisu Kwon, and Daejin Park.

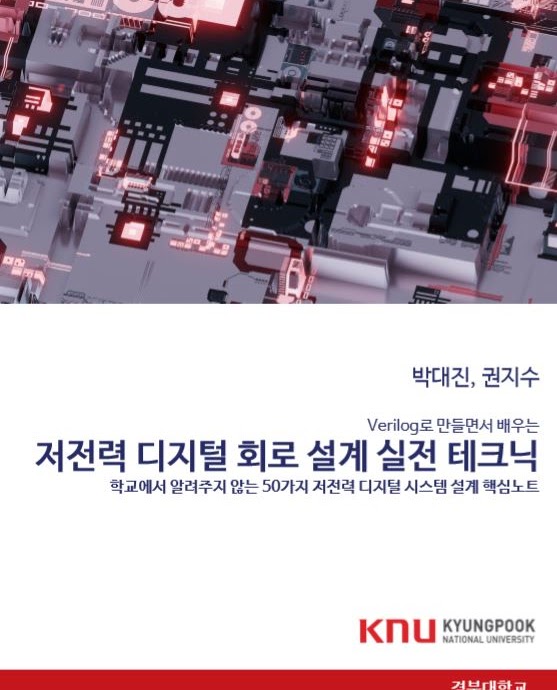

7️⃣ Books and Chapters

Low-Power Digital System Design - Practical Approach, TNES, 2021.

Daejin Park, and Jisu Kwon

- This book covers low-power system-on-chip design methodologies and implementation techniques, from gate-level to architectural approach and software-hardware interfaces:

- Toggle minimization in CMOS, gate, RTL, architecture, and software level.

- Clock gating, data filtering-based toggle propagation minimization

- Edge-triggered event-driven approach to reduce the active circuits

- Multi-clock domain and asynchronous circuit design techniques using buffers.

- Synchronizer between clock-crossing regions

- Power-gating and architectural circuit design method

📰 Patents

KRFirmware System to Control Software Malfunction and Control Method Thereof, Daejin Park, and Jisu Kwon, 2024.KRCode Insertion Module and Method for Dividing Storage of Frmware Segment, Daejin Park, and Jisu Kwon, 2022.KRFirmware Update Device and Update Method, Daejin Park, and Jisu Kwon, 2022.KRFirmware Update Method using QR Code Image and Electronic Device Performing Same, Daejin Park, and Jisu Kwon, 2022.

🎖 Honors and Awards

- 2023.09, Ph.D. Research Fellowship, National Research Foundation of Korea ($20k)

- 2019.03, B.S./M.S./Ph.D.-integrated course selected with early graduation (first student in university)

📖 Educations

- 2019.09 - Present, Ph.D. Student, Kyungpook National University, Daegu, South Korea.

- 2014.03 - 2019.08, Undergraduate, Kyungpook National University, Daegu, South Korea.

- 2011.03 - 2014.02, Keisung High School, Daegu, South Korea.

💬 Invited Talks

- 2023.08, PIM Semiconductor Research Center in KAIST - “Embedded C Programming for PIM Semiconductor”

- 2023.02, AI-Convergence ICT Research Group in KNU - “TinyML: Machine Learning World for Tiny Things”

💁 Services

- Journal Reviewer: Heliyon, Journal of Supercomputing, Sensors, Applied Sciences, JLPEA

🛠 Chips

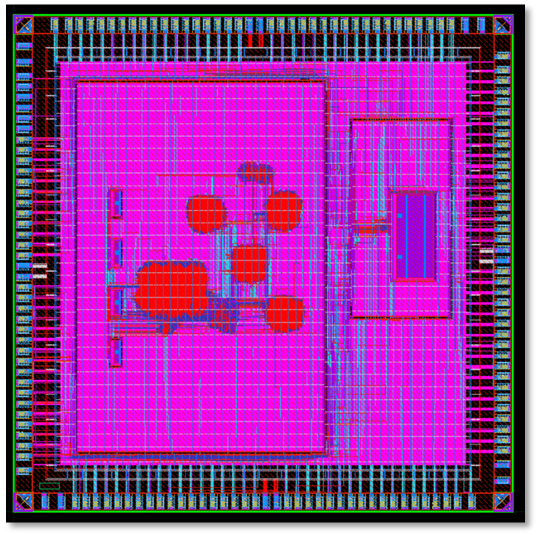

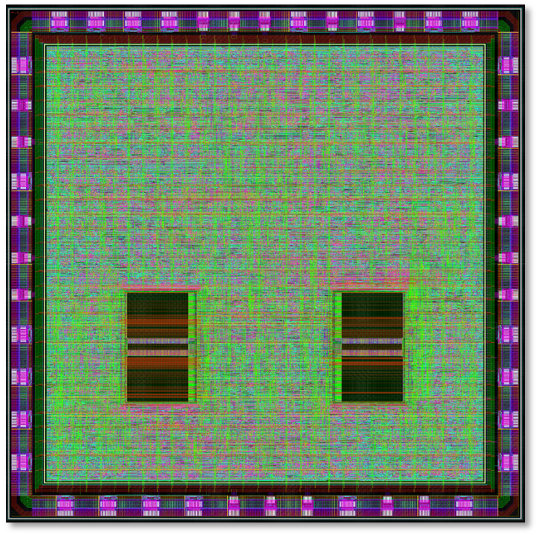

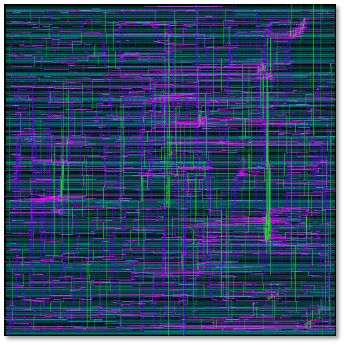

[Samsung 28nm] HAB-1

- Reconfigurable Bridge between Host and integrated CNN Accelerator

- Runtime bridge data transfer scheduling reconfigure support

- 2-channel MPI interfaces for accelerator control

- Extra MPI external slot for scalable accelerator expansion

[SK Key 130nm] InfiniTYle

- Arm Cortex-M0+ compatible custom ISA

- Custom SIMD instruction support

- Virtual scalable flash memory using off-chip QSPI interface

- 2-channel custom Tile-SoC interface for accelerator control

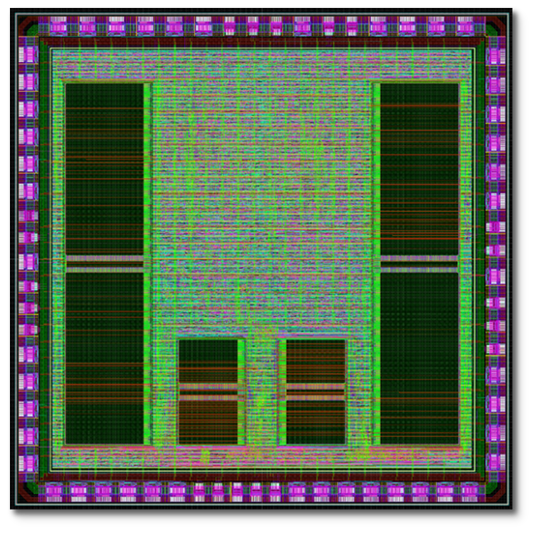

[SK Key 130nm] Tile-SoC

- Tile-connected scalable CNN accelerator

- Connect in all four directions (up, down, left, and right) for scalable extension

- Accelerator compute utilization-aware load allocation by host (= InfiniTYle)

[Confidential] DSI3 IP module for Ultrasonic Sensor

- Tri-level current decoding link layer

- Discovery mode support for daisy chain address assignment

- Receive voltage command from master / transfer current response to slave

- Periodic Data Collection Mode (PDCM) support

[Confidential] SENT IP module for Force Sensor

- Synchronization/Calibration pulse support

- Fast channel – Secure Message / High Speed Format support

- Slow channel – Short Serial Message / Enhanced Serial Message support

- Variable length pause pulse support

[DB HiTek 180nm] I2S IP module for AMBA peripheral

- APB DMA support

- External MCK, SCK, LRCK support

- Master/Slave and TX/RX support

- Small error LRCK frequency generation (22.05KHz, 44.1KHz, 48KHz, 96KHz, 192KHz)

- 2-types format support (Aligned, I2S)

- Mono channel support

- Interrupts support